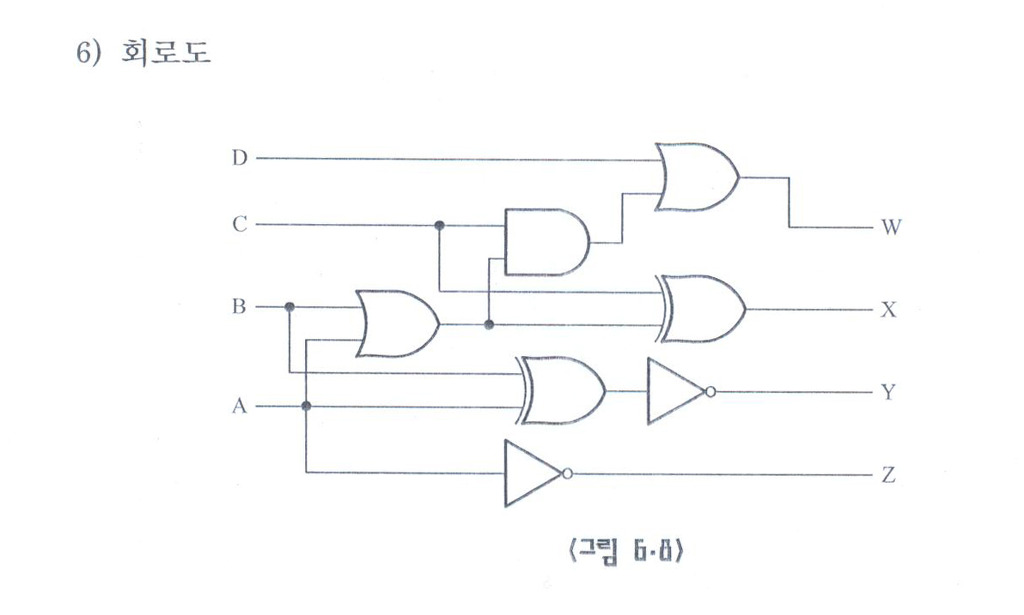

BCD-3초과코드 변환회로의 verilog HDL설계

2010, Nov 07

BCD코드를 3초과코드로 변환하는 회로를 VHDL로 설계하고,

진리치표대로 동작함을 확인하시오

//Stimulus for simple circuit

module stimcrct;

reg D,C,B,A;

wire W,X,Y,Z;

BCDto3 bcd2three(A,B,C,D,W,X,Y,Z);

initial

begin

D = 1'b0; C = 1'b0; B = 1'b0; A = 1'b0;

#100

D = 1'b0; C = 1'b0; B = 1'b0; A = 1'b1;

#100

D = 1'b0; C = 1'b0; B = 1'b1; A = 1'b0;

#100

D = 1'b0; C = 1'b0; B = 1'b1; A = 1'b1;

#100

D = 1'b0; C = 1'b1; B = 1'b0; A = 1'b0;

#100

D = 1'b0; C = 1'b1; B = 1'b0; A = 1'b1;

#100

D = 1'b0; C = 1'b1; B = 1'b1; A = 1'b0;

#100

D = 1'b0; C = 1'b1; B = 1'b1; A = 1'b1;

#100

D = 1'b1; C = 1'b0; B = 1'b0; A = 1'b0;

#100

D = 1'b1; C = 1'b0; B = 1'b0; A = 1'b1;

#100

$finish;

end

endmodule

//Description of circuit with delay

module BCDto3 (A,B,C,D,W,X,Y,Z);

input A,B,C,D;

output W,X,Y,Z;

wire x,y,z;

or g1(W,D,x);

and g2(x,C,y);

or g3(y,B,A);

xor g4(X,C,y);

xor g5(z,B,A);

not g6(Y,z);

not g7(Z,A);

endmodule